Physical Design

Physical Design

Physical Design

Physical Design is a crucial stage in semiconductor chip development where the abstract circuit (from the RTL or logical design) is transformed into a geometric representation that can be fabricated on silicon. It involves placing standard cells, routing interconnections, optimizing timing, and ensuring power and signal integrity. The goal of physical design is to create a layout that meets performance, area, and manufacturability requirements while adhering to design rules for the fabrication process.

01

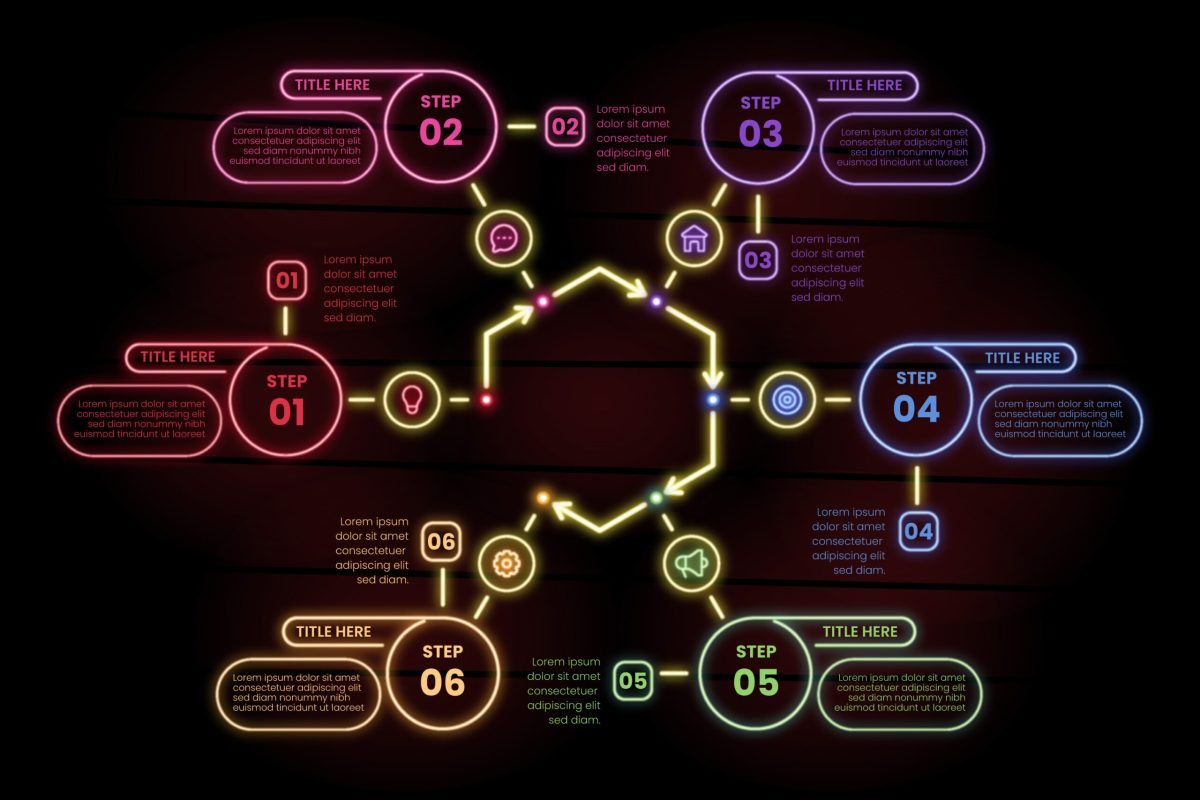

Complete RTL → GDSII Implementation Flow

We offer end-to-end backend design execution with strong methodology, automation, and sign-off expertise.

Our flow coverage includes:

• Synthesis to GDSII handoff

• Floorplanning and placement optimization

• Clock Tree Synthesis (CTS)

• Routing and congestion optimization

• Power planning and IR-drop analysis

• DRC/LVS/STA-based sign-off closure

7nm Process Node Experience

Hands-on expertise with 7nm FinFET technology, delivering PPA-optimized results by managing advanced-node challenges such as:

• Routing congestion & track-limited design rules

• Timing closure under multi-corner multi-mode scenarios

• EM/IR integrity management

• Advanced clocking, power intent & low-power design techniques

We bring in node-specific optimization strategies to accelerate convergence and reduce tape-out risks.